## **Design Note**

# Paralleling UCC3912 Electronic Circuit Breaker ICs By Paul Aloisi and Bill Andreycak

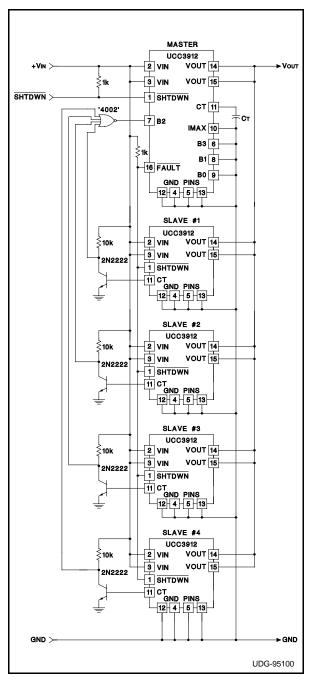

The UCC3912 IC is an integrated 3 Amp electronic circuit breaker which includes programmable overcurrent protection and retry timing following a fault. Other common uses for this function are in higher current (12A) and low "headroom" applications where a lower voltage drop is required. Each of these can be addressed by paralleling UCC3912 devices as shown in Figure 1.

To provide the circuit breaker function, the UCC3912 uses an internal FET switch having a typical on resistance of 0.150 ohms and 3 Amp continuous current rating. The positive temperature characteristics of MOS devices are beneficial in parallel applications to help divide the total load current evenly amongst all of the devices used. The UCC3912 with the lowest on resistance will pass slightly more of the current than the others, but its forward voltage drop will increase accordingly. This causes the load current to steer towards the other devices (in parallel) which were previously passing less current. With this configuration, equilibrium will be reached quickly as the total load current is distributed amongst all of the slaves.

One feature of the UCC3912 is its digitally programmable threshold for overcurrent limiting. When this current level is reached, the UCC3912 control circuitry regulates current to the programmed IMAX amplitude. To facilitate this, the gate drive to its internal MOS pass device is reduced, causing its on resistance and corresponding voltage drop to increase. As in the previous example for paralleled devices, this steers current to the other UCC3912s in parallel, forcing load sharing.

The duration of this allowable overcurrent condition is also programmable by selecting the appropriate timing capacitor value to the IC's fault timing (CT) pin. When the overcurrent condition is detected, two protection functions begin operation. First, the UCC3912 goes into a constant current mode to regulate current to the pro-

Figure 1. Paralleling UCC3912 Electronic Circuit Breakers

Design Note DN-68

grammed value of IMAX. Simultaneously, the device begins charging the fault timing capacitor and provides a digital indication at the open collector FAULT pin of the IC. The overcurrent duration concludes when the timing capacitor charges to a preset voltage and the MOS pass transistor is turned off. The off time is internally controlled to thirty times the programmed fault duration (tOFF = 30 • tFAULT), resulting in an approximate three percent (3%) effective duty cycle to safely limit power dissipation into a short circuit. Note that the UCC3912 also features internal overtemperature shutdown protection should the timer be incorrectly programmed for too long of a fault duration or inadequate heatsinking provided. Consult the UCC3912 datasheet for complete details of the timing and fault protection circuitry operation into single and repetitive overcurrent conditions.

#### **Circuit Operation**

In this paralleled application of UCC3912 devices, a master/slave arrangement will be incorporated and the fault timing control will be governed entirely by the master. Slave devices are configured to give a digital representation of the overcurrent condition, and their individual CT outputs are "NOR"ed together as an input to the master. A generic CMOS '4002 digital IC is used for its low current and 3V operational characteristics. Note that each input requires a 2N2222 NPN signal level transistor with a 10k ohm pull up resistor from the input supply (VIN) to its collector to complete the interface. This arrangement is necessary to achieve the proper digital inputs to the NOR gate while clamping the UCC3912 CT pin voltages to just a base-emitter diode drop (VBE) above ground. This will override the internal timing circuits of the individual slaves which are being controlled by the master's fault

In normal operation (prior to any overcurrent condition) the CT pin of each slave UCC3912 is low and the corresponding NPN transistor is off. The 10k ohm collector resistors place a digital high on the NOR gate's four inputs, and the output of this gate is low. When any of the slave UCC3912 devices goes into overcurrent protec-

tion its CT pin is pulled high by an internal current source. Normally, this would start charging the fault timing capacitor, but in this paralleled application, it forward biases the base-emitter junction of the respective 2N2222 transistor. This turns on the NPN device and forces a digital low input to the NOR gate. When all four of the NOR inputs go low, the output of the NOR gate goes high. This indicates that all four of the slaves are limiting current to their programmed maximum level and that an overcurrent condition exists.

The output of this NOR gate is used to digitally program one bit (BIT2) of the master UCC3912's overcurrent limit. The master was previously "off", not providing any load current since it's four overcurrent inputs (BITs 0 through 3) were all low. Any digital input below "0100" programs its output current to zero by turning off the power switch. But triggered by the overcurrent conditions of the slaves, the NOR gate output switches BIT2 of the master high. This turns the master on and programs its output current to 0.25A by the "0100" code at BITS 0 through 3. The master now allows 0.25 amps in addition to the slaves 12 amps to the load for a system total of 12.25A. This is the sum of the master (0.25A) and the four slave overcurrent programming thresholds of three amps each (4 • 3.0A). Provided that the demanded load current is in excess of 12.25 amps, as would be the case with a short circuited load, the master then provides two functions. First, it regulates the current through the master to the programmed 0.25 amp level. Additionally, it begins a fault timing sequence, the duration of which is programmed by the value of the fault timing capacitor, CT. This capacitor charges during the overcurrent condition until it reaches the internal 1.5 volt fault threshold. Once triggered, the fault latch turns off the UCC3912's internal MOSFET switch (to provide the circuit breaker function) while also indicating the fault condition by providing a "low" on the IC's FAULT pin. Note that the master's FAULT output is connected to the slaved UCC3912s' SHTDWN pin which turns off all of the slaved devices at the same time that the master turns off.

Design Note DN-68

The duration of the overcurrent event is programmed entirely by the master's CT timing capacitor value according to the UCC3912 datasheet information and design equations. The timing circuitry will deliver a current limited, pulsed mode fault protection and retry with a three percent (3%) duty cycle. While the timing capacitor is charging, each IC regulates and compares its load current to the programmed fault overcurrent level. Providing that the fault condition does exist, all UCC3912 ICs are turned off for the remaining ninety-seven percent (97%) of the programmed fault timing period. The resulting three percent duty cycle fault mode facilitates safe operation into a continuous overload or short circuited condition. It safely limits input power consumption and power dissipation in the circuit breaker switches. Additionally, no costly system downtime or manual replacement of a fuse or resetting of a circuit breaker is required.

Once the abnormal load condition has been removed, the circuit goes back into normal operation. The master's FAULT output returns to a "high" along with each of the slaves' SHTDWN inputs. If the load has not been removed, the master is retriggered by the NOR gate once each slave has detected an overcurrent condition, and the system goes back to the three percent duty cycle protection mode.

Note that the entire system is nominally triggered at 12.25A which is programmed by the four UCC3912 slaves' individual 3A thresholds and the 0.25A contribution of the master. However, this is unlikely to occur in a typical application because of two of the device's other ratings. First, is the maximum specified "trip" current of 3.5A for each slave switch and 0.45A for the master with the programmed overcurrent inputs (Bits 0 - 3). This would raise the highest trigger threshold to 14.45A. However, the more dominant factor is the high current capability of the UCC3912's switch which - is rated at four amps (4A) typical. In fact, each device can safely provide 5.2A (worst case) over all rated temperature and manufacturing conditions. One possible scenario should be reviewed using an instantaneous short circuit on the outputs. Even though all of the slaves properly triggered their internal fault logic at 3.5A (worst case), all four of the slaves could be delivering as much as 5.2 amps maximum (within the device's ratings) to the load. This would correspond to a maximum load current of 21.25 amps. And while unlikely to repetitively occur in a typical application, it does represent the worst case sum of the four slaves'(4 • 5.2A) plus the master's (0.45A) maximum current ratings. However, it's advised to evaluate this figure to that of other fault protection and overcurrent techniques, for example fuses, which can be significantly higher for short durations. More specific details and comparisons can be found in Unitrode Application Note U-151.

### Other Applications

This design example utilized the UCC3912 device's rated current capability of 3A, but can be scaled for other applications with higher or lower requirements. Each slave can be individually programmed for a maximum current between 0.25A and 3A in 0.25A increments using the 4 bit digital inputs to the fault circuitry. This is beneficial in many low voltage supply applications which require a low headroom or dropout voltage (the voltage drop between the input and output connections of the circuit breaker) to meet the load's power supply specifications. In these, the UCC3912's could be paralleled to minimize the series voltage drop - and not to obtain the higher current capability of the system. This is one application where it is desirable to program the slave's overcurrent thresholds to a lower value than 3A each.

The 0.25A example of additional load current provided by the master can also be raised to deliver higher total system current to accommodate a transient load condition. Examples of this can be found in many battery powered energy management systems where only the required active circuitry is enabled and all others are switched off. When supplying power to these types of loads, often high inrush currents are needed to quickly charge up any local bypassing and filtering capacitors. This brief condition can be accommodated by programming the master UCC3912's overcurrent bits accordingly.

Design Note DN-68

Although switching of only the master UCC3912's BIT2 is shown, its BIT3 input can also be switched for higher current capability. Additionally, BIT0 and BIT1 are shown grounded in the example circuit but can be programmed or switched with digital "1"s as well. Active digital programming of the master and all slave overcurrent BITs is also possible for the more demanding overcurrent protection applications. Each UCC3912 Electronic Circuit Breaker IC also features internal overtemperature protection with shutdown for complete system protection.

#### **Additional Reference Material:**

- [1] UCC3912 Data Sheet

- [2] Application Note U-151: "UCC3912 Programmable Electronic Circuit Breaker – Performance Evaluation and Programming Information"

- [3] UCC3912 Evaluation Kit

- [4] Design Note DN-58: "UCC3912 Programmable Electronic Circuit Breaker Performance Evaluation and Programming Information"